Verzia pre tlač

Verzia pre tlač

Začiatky s VHDL

Zobrazovanie hodnoty z externého AD prevodníka na 7-segmentovom LCD displeji

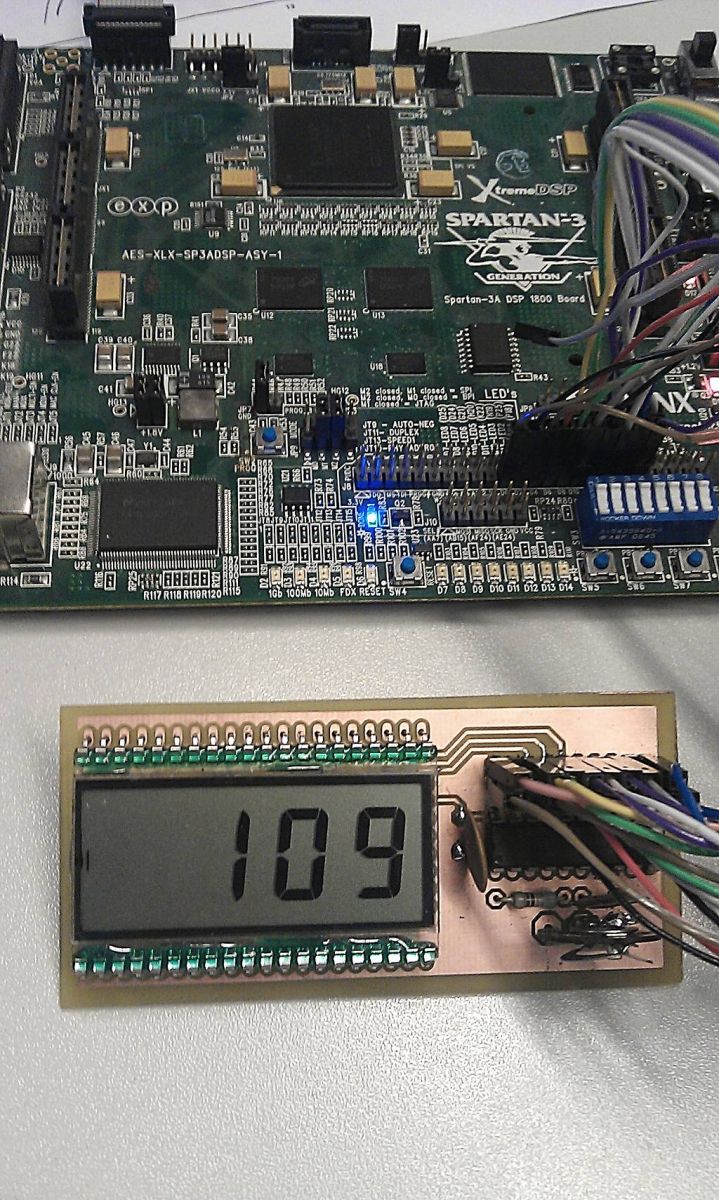

Na Žilinskej univerzite sme na inžinierskom stupni absolvovali predmet Návrh zákazníckych integrovaných obvodov, kde sme sa zoznámili s FPGA firmy Xilinx, konkrétne sme pracovali s vývojovou doskou Spartan-3A 1800 DSP. Ku FPGA Xilinx je poskytovaná free verzia programu Xilinx ISE, v ktorej sme písali program v jazyku VHDL a simulovali činnosť programu. Mojou úlohou bolo zostrojiť zariadenie schopné čítať hodnotu z paralelného 8-bitového AD prevodníka a zobrazovať ju na 7-segmentovom LCD displeji.

Tento článok má slúžiť hlavne ako názorná ukážka ako prebieha realizácia zapojenia pre FPGA a programovanie v jazyku VHDL.

1 Realizácia zapojenia

Pri koncepcii zariadenia som vychádzal zväčša katalógových listov výrobcov a vlastných skúseností.

Celé zariadenie možno rozdeliť na dva hlavné bloky:

– Blok riadenia a čítania dát z AD prevodníka

– Blok riadenia LCD displeja

Prepojenie s vývojovou doskou Spartan-3A je realizované pomocou 20pin konektora, ktorý slúži zároveň aj na napájanie.

Schému zapojenia a DPS v programe Eagle 6.2 si môžete stiahnúť: fpga_meter.zip

1.1 Blok riadenia a čítania dát z AD prevodníka

Tento blok sa stará o riadenie a čítanie dát z AD prevodníka ADC 0804. Na komunikáciu sa využívajú 4 riadiace signály – WR,RD,CS, a INTR a 8 dátových signálov D0-D7. AD prevodník potrebuje pre svoju činnosť minimum externých súčiastok, v minimálnej konfigurácií stačí len RC kombinácia pre generovanie frekvencie vnútorného oscilátora. Štandardné napájanie AD prevodníka je 5V. Pri tomto napájacom napätí sa nastaví pomocou interného deliča referenčné napätie 2,5V.

Ja som na dosku doplnil aj odporový trimer pomocou ktorého možno privádzať rôzne hodnoty napätia na vstup AD prevodníka a tým demonštrovať jeho činnosť.

Čítanie dát s AD prevodníka prebieha nasledovne:

1) Signály CS a WR sa privedú do log. 0 po dĺžku minimálne 100ns

2) Čaká sa na signál INTR z AD prevodníka, ktorý oznamuje riadiacej aplikácií, že prevod je skončený

3) Signály CS a RD sa privedú do log. 0 a v tomto stave sa prečítajú dáta z AD prevodníka paralelne pomocou pinov D0-D7.

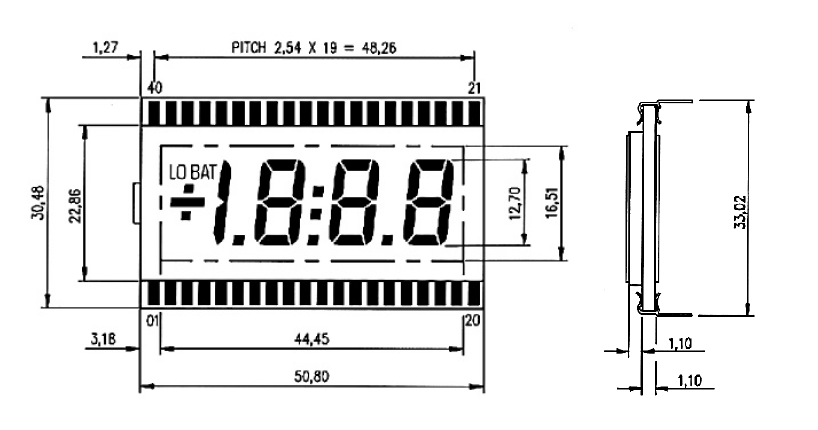

Časovanie je zrejmé aj s Obr. 1.

Obr. 1. – Časovanie AD prevodníka

1.2. Blok riadenia LCD displeja

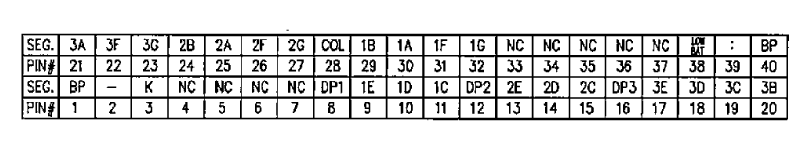

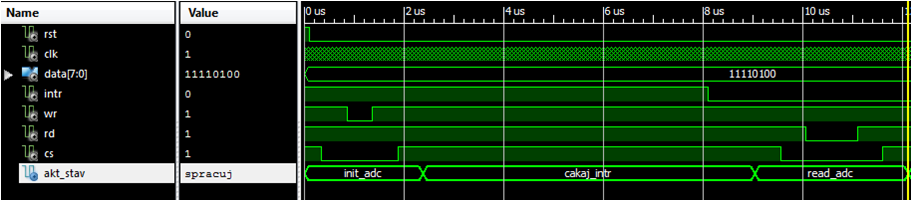

Na riadenie 3,5miestneho 7-segmentového LCD displeja som sa rozhodol použiť tri posuvné registre 4094, ktoré dokážu ovládať 3 číslice LCD displeja. Vďaka tomu sú potrebne na riadenie len 4 vodiče. Rozmery a rozmiestnenie pinov displeja je možno vidieť na Obr. 2. Priradenie jednotlivých pinov ku segmentom displeja je zrejmé z Obr. 3. Pin z označením BP je spoločná elektróda všetkých segmentov.

Zobrazenie jednotlivých segmentov sa realizuje striedavým napätím amplitúdy 5Všš a frekvencií 30Hz na daný segment oproti spoločnej elektróde BP.

Obr. 2. – Špecifikácia rozmerov a pinov LCD displeja

Obr. 3. – Priradenie segmentov jednotlivým pinom dispeleja

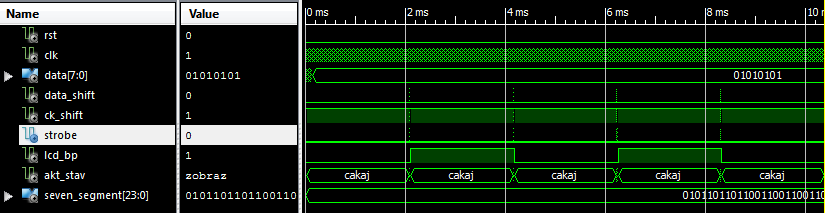

Na riadenie posuvného registra sú použité signály CLK, DATA a STROBE. Vstupné dáta privádzame na pin DATA, kde sú snímané nábežnou hranou CLK hodinového signálu. Po vyslaní všetkých dát možeme aktivovať výstupy posuvných registrov privedením signálu STROBE do log. 0.

2 POPIS PROGRAMU

Program v jazyku VHDL je písaný systémom stavových automatov.

Program obsahuje 6 stavov:

– INIT_ADC

– CAKAJ_INTR

– READ_ADC

– SPRACUJ

– ZOBRAZ

– CAKAJ

Tieto stavy sa prepínajú na základe postupnosti vykonávania daných úloh.

Kompletný program v jazyku VHDL si možete priezrieť v nasledovnom odkaze: https://pastebin.com/FZ6tnkk3

Po signále reset sa nastaví ako východiskový stav INIT_ADC, ktorý zabezpečí správne vyslanie riadiacich signálov WR a CS pre spracovanie vzorky AD prevodníka. Po vykonaní tohto stavu sa nastaví nasledovný stav na CAKAJ_INTR, ktorý sa vykonáva dovtedy, pokiaľ sa vstupný signál INTR nenastaví do log. 0, čo nás informuje o skončení prevodu. Po príchode tohto signálu sa ako nasledovný stav nastaví READ_ADC, ktorý zabezpečí vyslanie riadiacich signálov RD a CS a následne prečítanie hodnoty AD prevodníka pomocou dátových vodičov D0-D7. Vykonávanie tejto sekvencie je zobrazené na Obr. 3.

Obr. 3 – Sekvencia čítania s AD prevodníka

Po skončení tohto stavu nasleduje stav SPRACUJ, ktorý najskôr prevedie 8-bitové binárne číslo do BCD kódu a následne skonvertuje BCD kód do kódu pre riadenie 7-segmentového displeja. Keď sa táto operácia dokončí nastaví sa stav ZOBRAZ, ktorý sa stará o zobrazenie dát na 7-segmentovom displeji.

V stave ZOBRAZ sa najskôr nahrajú dáta do posuvného registra. Po ich nahraní sa aktivuje výstup posuvných registrov privedením signálu STROBE do log. 0 a signál LCD_BP sa nastaví tak, aby u segmentov, ktoré sa majú zobraziť bola negovaná logická úroveň. Nasledovný stav sa nastaví na CAKAJ, ktorý zabezpečí čakací čas približne 2ms. Túto sekvenciu možno vidieť na Obr. 4.

Obr. 4 – Sekvencia zápisu do posuvných registrov

Po ich uplynutí sa znova nastaví stav ZOBRAZ, teda znova sa vyšlú dáta do posuvných registrov, tento krát však negované nakoľko musíme zabezpečiť budenie striedavým napätím, teda aj signál LCD_BP sa zneguje. Tento proces sa opakuje zhruba 200ms. Po tomto čase sa stav nastaví na INIT_ADC čím sa celý proces znova zopakuje. Na Obr. 5 možno vidieť proces budenia LCD displeja, pomocou signálu LCD_BP s periódou zhruba 2ms.

Fotografia hotového výrobku

- Novinky na webe SVETELEKTRO - 12. decembra 2020

- TEPLOMĚR DO UDÍRNY - 21. júla 2020

- Výsledky súťaže o najlepší výrobok–4. kolo - 23. decembra 2019

Komentáre (6)

Pridaj komentár

Prepáčte, ale pred zanechaním komentára sa musíte prihlásiť.

aká náhoda, dnes mi prišli akurát knihy o programovaní vo VHDL a akurát som pozeral spracovanie A/D prevodu a jeho zaokruhlovanie

možno by sa zišlo založiť tému na fóre o CPLD a FPGA

Mam ktomu jednu kozmeticku poznamku original zdrojak by nemal byt hostovany iba na pastebin.com moze expirovat a byt link nasledne nefunkcny.

Rozbehnite si attachmenty alebo source-plugin a nech je to hostovane na svetelektro.com clanok bude mat urcite dlhsiu zivotnost ako ten pastebin

Tyka sa to vsetkych odkazov na tomto peknom portaliku.

Ihmo co je to za logic analyzer co pouzivas ?

Ahoj na Pastebin som nastavil ze chcem aby zdrojovy kod neexpiroval nikdy, ale mas pravdu ze mozu mat nejaku poruchu servera a sme nahraty 🙂 Pokusim sa do buducna to davat vsetko sem.

Cosa tyka toho logickeho naalyzera tak je to priamo sucast programu ISE webpack, cize je to sotwarova zalezitost.

Odporúčam príklady na http://www.myhdl.org/doku.php .. je to jazyk vytvorený z Pythonu na popis HDL ktorý je možné preložiť do VHDL/Verliogu..

Urobil som v ňom FW pre Xilinx Spartan 6 na svoju bakalárku (digitálny osciloskop s vzorkovaním na 125MHz) a funguje to krásne.. viac (https://svetelektro.com/Forum/fpga-kit-s-modulom-digitalneho-osciloskopu-a-log-analyzatoru-t31646.html)

Výhodou je že k základnému simulačnemu HDL vývoju/testovaniu netreba celé ISE ale stačí Python, MyHDL a GTKWave čo má spolu asi 50MB a je to celé pohotovejšie + je možné písať veľmi dobré unit testy na simulovaný HW…

A ďaľšia vec je subjektívne vyššia produktivita voči VHDL —> python je predsalen jednoduchší syntaxov… Pritom nejako výrazová sila nie je omezená oproti VHDL/Verilog… ale to isté vo VHDL napíšem skoro na dvojnásobok riadkov čo v MyHDL …

Na hore odkazovanej stránke je kopec príkladov od jednoduchých (blikanie) až po zložitejšie ako Sigma-Delta DAC alebo FFT.

Prosím ťa, aký nástroj používaš na download programu do CPLD a FPGA? Potreboval by som naprogramovať jedno CPLD a urobil som si paralelný programátor cez JTAG, ktorý je kompatibilný s ISE webpackom.

http://vsdev.me/media/projects

/xilinx_jtag_download_cable_schematic.png

To ISE sa mi zdá zbytočne veľké, niekoľko GB.

No ak je to Xilinxácke zariadenie tak sa ISE nevyhneš ak nemáš teda hotový bitstream, ak áno tak stačí SW iMPACT.