Verzia pre tlač

Verzia pre tlač

FPGA od zadania k produktu – Úvod I.

Séria článkov o technológii FPGA bude popisovať môj subjektívny pohľad na vývoj zariadenia s využitím FPGA.

Články budú vysvetľovať aplikáciu v projekte osciloskopu/log. analyzátoru uverejnenom na fóre [1] a na githube [2] (kde je možné nájsť kompletné zdrojové kódy a schémy/dosky v Eagle). V prvej časti však najprv uvediem samotnú technológiu FPGA a základné informácie o spôsobe vývoja aplikácií s FPGA.

Čo je možné s FPGA vytvoriť?

Pre predstavu veľkosti dnešných FPGA okrem uvedeného projektu [1][2] je možné vytvárať aj podstatne zložitejší HW vo FPGA a to napr. kompletnú AMIGA 500 [3] v pomerne malom (low-end) FPGA alebo Apple II [4] alebo aj napr. celé Pentium. Ďalším veľkým pôsobiskom je spracovanie signálov (DSP) a bývajú často súčasťou ARMových SoC. Najnovšie sa využívajú ako výkonný „miner“ v sieti Bitcoin [5].

Obr. 1- Amiga 500 vo FPGA Obr. 2 – Apple II v FPGA

Takže skutočne sa fantázii medze nekladú a do FPGA správnej kategórie sa dneska „vojde“ takmer všetko!

Čo je to FPGA?

FPGA alebo Field Programmable Gate Array teda na mieste (v obvode) programovateľné hradlové pole umožňuje vytvoriť ľubovoľný digitálny obvod (s obmedzením na počet logických obvodov, ktorými disponuje). Sám o sebe nedokáže vykonávať žiadnu funkciu na rozdiel od mikrokontroléra, ktorý disponuje rôznymi integrovanými modulmi (SPI, I2C, ADC, DAC atď.), FPGA väčšinou neobsahuje nič všetko je vytvárané programovateľnou logikou.

FPGA sú väčšinou volatilné zariadenia, to znamená že po vypnutí konfiguráciu (tzv. bitstream) „zabúdajú“ a bez konfigurácie po zapnutí sú úplne „mŕtve“. Preto pri FPGA väčšinu býva umiestnená FLASH pamäť, z ktorej si po zapnutí napájania FPGA konfiguráciu stiahne (Sú aj iné možnosti ako dostať konfiguráciu do FPGA, ale o tom neskôr).

S touto vlastnosťou treba rátať, pretože z toho vyplýva, že FPGA nie je okamžite po zapnutí funkčné a trvá desiatky až stovky ms kým „nabehne“.

Obyčajne FPGA disponujú vysokým počtom vývodov (stovky až tisícky), preto sú bežne FPGA najčastejšie v BGA púzdrach, čo práve znižuje možnosti amatérskeho použitia.

Aká je štruktúra FPGA?

Skladá sa v zásade z veľkej programovateľnej prepojovacej matice a logických blokov (na obrázku CLB) a programovateľných I/O. Táto základná štruktúra je často obohatená o DSP bloky, distribuovanú pamäť a ďalšie špecifické obvody podľa typu FPGA. Ďalej obsahuje PLL a DCM bloky na generovanie a správu hodín taktiež prepojovacia matica obsahuje špeciálne rozvody hodín.

Obr. 3 – architektúra FPGA

Configurable Logic Block (CLB)

CLB niekedy sa označuje LAB (Logic Array Block – rozdiel v terminológii je vo výrobcoch, Altera používa LAB a Xilinx CLB) obsahuje lookup tabuľky (LUT) s rôznym počtom vstupov (3, 4, 6) v závislosti od rodiny FPGA, táto tabuľka realizuje naprogramovanú logickú funkciu (kombinačný obvod). Ďalej plnú sčítačku (FA – Full Adder) a klopné obvody (DFF), ktoré umožňujú realizovať funkciu sekvenčných obvodov a multiplexory (mux) umožňujúce meniť dátovú cestu vnútri CLB.

Obr. 4 – CLB (LAB)

I/O bloky

Starajú sa o komunikáciu s okolným svetom FPGA, umožňujú pomerne pokročilé nastavenia od logickej úrovne, pullup/pulldown k diferenciálnym párom a špeciálnym rozhraním pre pamäte DDR2/DDR3. Tu zase schopnosti závisia od zvolenej rodiny FPGA.

Programovanie FPGA

Vzhľadom na vysokú zložitosť, nie je praktické priamo tvoriť návrh na úrovni prepojení CLB a programovaní LUT. Preto sa využíva popisu na vyššej úrovni a k tomu je možné použiť klasickú logickú schému alebo HDL jazyky. Najčastejšie vzniká popis práve prostredníctvom HDL jazyku.

HDL jazyky (Hardware Description Language)

Základným cieľom týchto jazykov je popísať digitálny obvod. Na rozdiel od konvenčných jazykov sa tu kód nevykonáva (výnimkou je simulácia), ale je z neho odvodená konfigurácia FPGA. Ďalším rozdielom je masívne paralelný priebeh. K tomuto účelu sa využíva konceptu tzv. procesov a signálov.

Príklad zápisu dvoch procesov v jazyku MyHDL:

to isté vo VHDL:

Tento príklad ukazuje dvojicu procesov, ktoré prebiehajú paralelne, kde prvý proces popisuje sekvenčný obvod – čítač, ktorý je použitý ako delič frekvencie. Druhý proces popisuje kombinačnú logiku, kde signál halfMhzClock je vyvedený do signálu clkDacOut len ak je aktívne povolenie signálom clkEn.

Signál sa teda dá predstaviť ako vodič spájajúci logické obvody (platia teda isté obmedzenia ako v prípade skutočného obvodu – zapisovať do jedného signálu (priradiť hodnotu) môže len jeden proces. A zároveň signál môže nadobúdať okrem 0 a 1 špeciálne stavy a to napr. ‚Z‘ – stav vysokej impedancie (využitie je napr. radič I2C, zdieľaná zbernica) alebo ‚X‘ – skrat, ‚U‘ – nedefinovaná hodnota a ďalšie.

Procesy je možné si predstaviť ako logické obvody, ktoré signály prepájajú.

Z príkladu je možné vidieť, že rozdiely medzi HDL jazykmi sú skôr kozmetické a otázka osobnej preferencie, MyHDL preferujem hlavne z dôvodu flexibility a úspornejšieho zápisu oproti VHDL a lepšej čitateľnosti oproti Verilogu.

Vznik konfigurácie FPGA z HDL popisu

Je zrejmé že popis v HDL musí byť spracovaný na konfiguráciu logických blokov a ich prepojenia. O toto sa našťastie starajú nástroje, ktoré poskytujú výrobcovia FPGA.

Spracovanie HDL prebieha v zásade 3 krokoch a to:

1. Syntéza:

Táto časť analyzuje HDL popis a hľadá hardwarové ekvivalenty zápisu v HDL. Napr. na zápis procesu clockDivisor nájde 7-bitový čítač.

Ďalšími príkladmi môže byť posuvný register, konečný automat, dvojportová pamäť…

2. Mapovanie na cieľovú technológiu:

Tu už prichádza k slovu konkrétne vybratý model FPGA a mapper sa snaží nájsť najbližšie/najspornejšie/najrýchlejšie (podľa nastavení mappera) ekvivalenty v syntéze nájdených komponentov v zvolenom FPGA.

V tejto časti poznať či sa dizajn „vojde“ do FPGA a či je vôbec možné v danom type FPGA daný popis v HDL vytvoriť.

3. Place and Route:

V tejto fáze sa hľadá vhodné usporiadanie a prepojenie jednotlivých komponentov FPGA v prepojovacej matici. Tu sa rieši hlavne časovanie tzv. static timing analysis, ktorá určí či návrh bude fungovať na zvolenej frekvencii (a iných časovacích obmedzeniach napr. hold/setup time).

Rozloženie a prepoje je možné samozrejme ručne ovplyvniť a to v jednoduchosti zmenou optimalizačnej stratégie a v zložitosti priamo ručným routovaním.

Tento proces je pomerne zložitý a skrýva hneď niekoľko problémov. V prvej fáze môže nastať to že syntetizátor nesprávne rozpozná popis a zvolí inú HW implementáciu ako autor HDL popisu zamýšľal, na toto narážajú najmä začiatočníci a prejavuje sa to tým že vec v simulácii perfektne funguje, ale v realite v FPGA už nie.

Druhým problémom, ktorý súvisí ako s bodom 2 tak s bodom 3 je časovanie, ak vybraté komponenty vo fáze 2 majú príliš veľké oneskorenie a dizajn obsahuje veľa prepojení tak vo fáze 3 nie je možné dodržať stanovené časovacie obmedzenia a je nutné sa buď uspokojiť s nižšou pracovnou frekvenciou alebo dizajn premyslieť (napr. zaviesť zreťazenie, obmedziť množstvo kombinačnej logiky, presvedčiť mapper aby použil iné komponenty – napr. použitie distribuovanej RAM namiesto FIFO).

IP Cores

Našťastie však netreba všetko vytvárať od nuly, priamo výrobcovia FPGA ponúkajú množstvo tzv. IP cores, ktoré predstavujú hotové odladené obvody, príkladom môže byť IP Core ChipScope od Xilinxu ktoré umožňuje mať logický analyzátor priamo v FPGA, ktorý komunikuje cez JTAG z Xilinxovým SW. Ale možností je veľa napr. kontroléry DDR2/3 pamätí alebo dokonca kompletné mikrokontroléry ako kompletné portfólio AVR.

Nahratie konfigurácie do FPGA

Po úspešnom P&R už zostáva len vytvorený „bitstream“ nahrať do flash pamäte z ktorej FPGA konfiguráciu načíta.

Záver

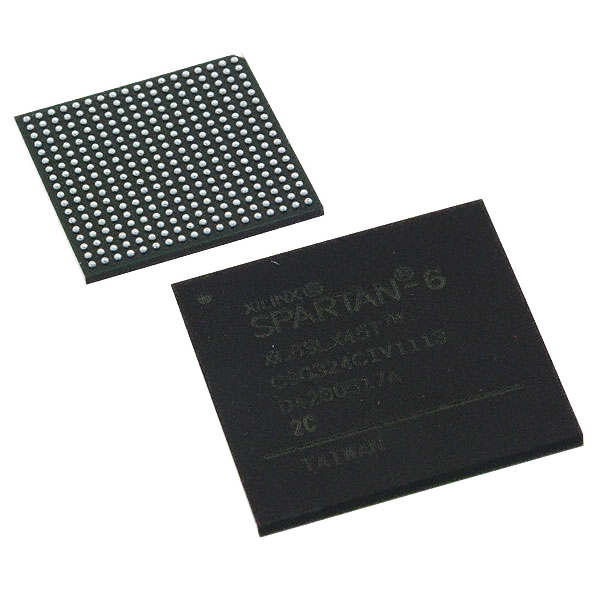

Týmto tento teoretickejší diel uzatváram a môžete sa tešiť na ďalší – praktickejší diel, ktorý sa bude zaoberať návrhom zapojenia a dosky pre FPGA obvodu zobrazeného na nasledujúcej fotke:

- FPGA od zadania k produktu – Hardware II. - 5. septembra 2013

- FPGA od zadania k produktu – Úvod I. - 19. augusta 2013

Komentáre (10)

Pridaj komentár

Prepáčte, ale pred zanechaním komentára sa musíte prihlásiť.

No, som zvedavy na pokracovanie, zaciatok vyzera slubne.

Tiez sa neiem dockat. Dufam ze pojdes viac do hlbky ako len standardny uvod 😉

Jasne.. toto je taký začiatok zľahka aby sa poniektorí nezľakli hneď v prvom diely…

Ďaľší bude zapojenie (aj keď to si myslím že tu sú aj fundovanejší ľudia na to, ale čo viem to odovzdám) a potom samotný FW (HDL) vývoj a ako to skĺbiť aby to komunikovalo s C++ na PC na rozumnej rýchlosti (USB 2.0) :).

Myslim ze tych uplnych zaciatocnikov si uz dostatocne vydesil tou BGA potvorou na doske 😉

A ty ostatny co uz maju nieco za sebou vedia o co sa jedna takze preto radsej viac do hlbky.

Tak ide to aj bez BGA potvory ale to je potom TQFP144 (a viac) potvora takže prašť jak uhoď.. Na hĺbku si nechávam ostatné diely.. niekde treba začať 🙂

TQFP144 je v pohode na domace bastlenie. Mam to na plosaku zaspajkovane rychlejsie nez DIP40 🙂

No ak máš dosku s maskou tak iste, to povrchové napätie kvapalín je krása a diery sú proste otravná záležitosť.. Ja osobne som bol ale rád keď som ručne zapájkoval TSSOP48.. no skrátka radšej mám pick&place a reflow ako sa s tým ******.

Ono zas na druhú stranu dá sa aj BGA osadiť doma, ale úspešnosť asi nebude úplne 100%. Ale hlavne asi už nie na doma vyrobenú dosku…

tiež sa teším na pokračovanie, už rok som pripravený a vybavený na štúdium FPGA, len akosi nie a nie zohnať poslednú súčiastku , teda čas. ale to je asi dosť vzácny a prchavý artikel.

Tak to súhlasím… čas to je vždy problém.. ja som za celé leto sa k nejakému laborovaniu s tým FPGA už nedostal a je tam pár vecí ktoré by som chcel napr programovanie priamo cez USB a nie cez JTAG programátor od Xilinxu, ktorý zbytočne drahý.. teraz vyspravujem auto nech mi ho hrdza nezožerie (bolo to horšie než to vyzeralo tak sa to natiahlo, snáď zajtra bude hotovo) tak článok som odložil a dúfam že tento víkend bude (cca polka už je napísaná ale chcem to spraviť podrobne tak bude asi 2x tak dlhý ako tento :)).

No paráda, když koukam na ebay, pořád tam vidím programátory a další hračky pro FPGA a následující semestr se s nima budeme zabývat, tak jsem zvedavej a tenhle seriál mi bude určitě ku prospěchu 🙂