Verzia pre tlač

Verzia pre tlač

FPGA od zadania k produktu – Hardware II.

V sľúbenom pokračovaní sa dozviete ako vzniká aplikácia FPGA z obvodového pohľadu.

Najskôr sa však pozrieme na samotné zadanie, potom uvediem obvodový návrh a následne návrh dosiek.

Vopred upozorňujem, že čo sa týka návrhu dosky je to moja prvotina takže ak niekto opraví/upresní/vylepší moje tvrdenia, tak budem len rád :). Ďaľším upozornením je, že nebolo/nebude možné pokryť všetko, čo viedlo k zdárnemu riešeniu, pretože len k zvolenému FPGA je niekoľko datasheetov po stovkách strán, takže sa nedá zhustiť z toho všetky skúsenosti .Avšak po ich prečítaní by vám malo byť jasné ako navrhnúť jednoduchý obvod s FPGA.

Zadanie

Zadanie znelo obecne „Osciloskop na báze obvodov FPGA“, ja som určil doplňujúce parametre a to, že bude disponovať 16-bit. log. analyzátorom, bude mať 2 kanály a vzorkovanie bude pre začiatok aspoň na 100MHz a bude použitý ako USB osciloskop.

Celková koncepcia

Výsledkom je základná koncepcia čo zariadenie bude obsahovať. Rozhodol som sa, že FPGA časť a analógová časť bude na samostatných doskách. V zásade potrebujeme na osciloskopové kanály AD prevodníky (ADC), pre ne predzosiľňovače a transceiver poslúži ako logičák. Tieto komponenty sú riadené pomocou FPGA a posielajú dáta do FPGA. Na ukladanie vzorkov potrebujeme pamäť (SDRAM) a na komunikáciu s PC USB čip (USB).

FPGA časť

Koncepcia

Najskôr si ujasníme koncepciu dosky s FPGA. Zo zadania vyplýva, že budeme potrebovať FPGA, hodila by sa nejaká pamäť FLASH na uloženie konfigurácie FPGA (ako vyplýva z predošlého článku [1]), samozrejme operačná pamäť na ukladanie vzorkov, čip USB komunikácie s PC (zabezpečí odosielanie nameraných dát a ovládanie zariadenia z PC, prípadne programovanie FPGA).

Obr. 2– Koncepcia FPGA dosky

Určite potrebujeme prepájacie konektory na ďalšiu dosku, na ktorú budú vyvedené I/O FPGAčka. Ďalej potrebujeme priame programovacie rozhranie, ktoré zabezpečuje konektor JTAG a v neposlednej rade napájacie zdroje. Doplnkom sú potom indikačné LED diódy, ktoré sa hodia pri oživovaní programovania FPGA a následnej aj aplikácie v FPGA.

FPGA – výber

Toto je pomerne obtiažna časť návrhu s dopredu nejasnými vecami. Prvou je, že ak nie je už dopredu hotový FW, tak nie je možné odhadnúť presný počet potrebnej logiky, ktorú má FPGA obsahovať. Ďalej treba mať ujasnený návrh aplikácie, na ktorú sa FPGA použije, aby bolo možné určiť požadovanú počet I/O.

Ja som sa obmedzil na firmu Xilinx, hlavne z dôvodu, že FPGA od Xilinx-u sme používali v škole na výukovom kite FITKIT [17] a teda v časovej tiesni bakalárskej práce som dopredu už poznal všetky nástroje a tiež z toho dôvodu, že portfólio Xilinx je najširšie.

Výber sa odvíjal hlavne od potrebného počtu I/O, staršia výbehová rodina Spartan 3 je vyrábaná v 208 pinovom vývodovom púzdre. Tento model je však už v ponuke dodávateľov pomerne drahý a jeho parametre (bloková pamäť, počet logických blokov) nie sú zrovna oslnivé. Problém je že Spartan 6 aj keď je výkonnejší ako Spartan 3 pri porovnateľnej cene, tak vo vývodovom púzdre TQFP má len 144 pinov a to nebolo na moju aplikáciu dostatočné. Takže výber padol na BGA púzdro a to konkrétne púzdro CSG324.

Model FPGA bol už čistý odhad, keďže som mal v čase navrhovania napísanú len časť FW tak sa to odzrkadlilo v zbytočne štedrom odhade a to zvolením modelu LX25, kde by pravdebodobne funkciu zastal aj model LX9, na druhú stranu s „prázdnym“ FPGA je možné dosiahnuť vyšších pracovných frekvencií.

Keď sa zaplnenie blíži k 100%, tak problémy s „routovaním“ logiky začínajú rapídne narastať. Tu sa dá jedine doporučiť najprv napísať FW a až potom odhadovať aké „veľké“ FPGA použiť, treba však vždy mať rezervu na ladenie (napr. použitie debuggovania pomocou Chipscope zaberie slušnú časť FPGA).

Programovanie a inicializácia FPGA

Programovanie

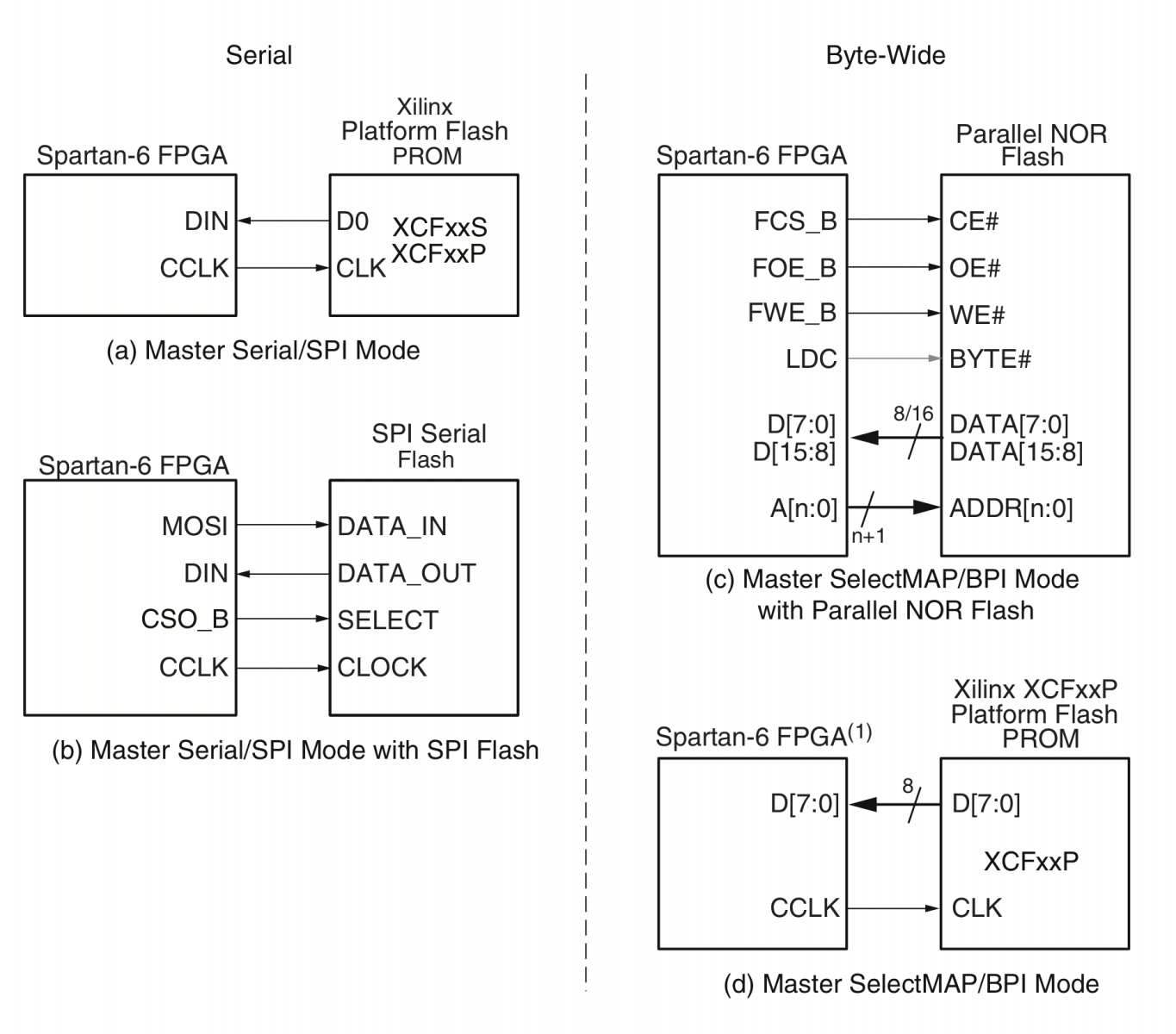

Ako som hovoril v minulom článku [1] FPGA musí po každom zapnutí previesť inicializáciu. Inicializácia prebieha obyčajne tak, že FPGA načíta konfiguráciu z externej pamäte (Master) (pozn. Sú modely FPGA, ktoré majú integrovanú FLASH pamäť napr. Actel Ignoo Nano – je to zároveň asi najmenšie vyrábané FPGA je dostupné aj v puzdre 3x3mm, ak by ste chceli vedieť o ňom viac tak odporúčam toto video [4]) Kde je možné využiť drahé sériové FLASH pamäte priamo od Xilinxu tzv. Platform Flash (a) alebo konvenčné SPI Flash (b). Potom to isté v paralelnom prevedení (c) a (d).

Obr. 3- Konfigurácia FPGA v režime Master

Druhou možnosťou je využitie zariadenia, ktoré konfiguráciu z externej pamäte do FPGA nahrá napr. MCU (Slave). Tu je možné využiť sériové (a) paralelné (c) rozhranie alebo priamo rozhranie JTAG (b).

Obr. 4- Konfigurácia v FPGA režime Slave

O programovaní FPGA Xilinx dodáva samostatný datasheet, ktorý je tu [2]. Sú v ňom vyčerpané všetky detaily k programovaniu, napr. ako spraviť tzv. „daisy chain“, kedy sa z jednej pamäte inicializuje niekoľko FPGA.

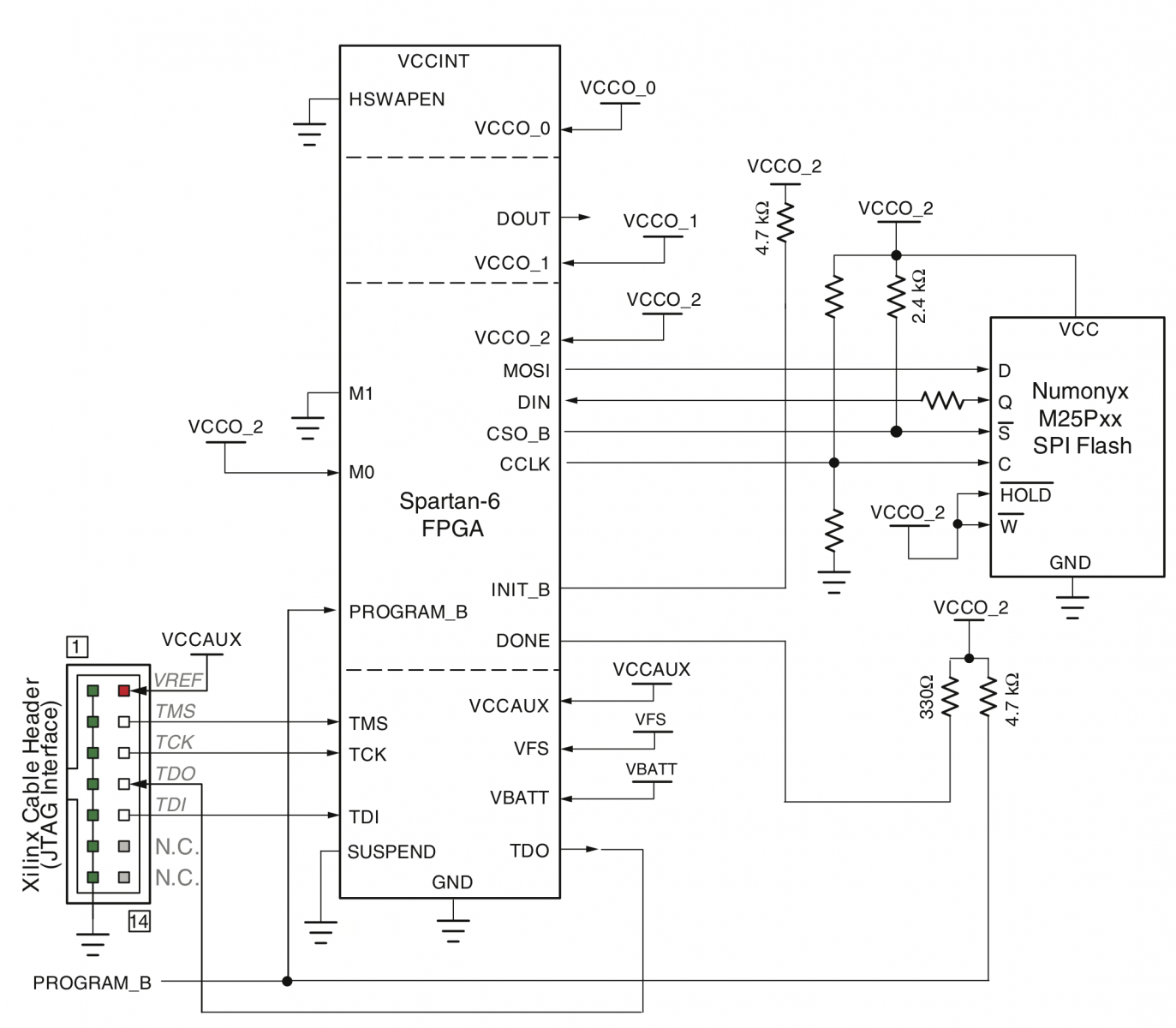

Použité riešenie bolo nakoniec mód Master serial s konvenčnou pamäťou FLASH a zároveň sprístupnený JTAG na programovanie v režime. Toto zapojenie uvádza priamo datasheet [2]. Zoznam podporovaných FLASH pamätí v tejto konfigurácii je možné nájsť tu [3], niektoré zdroje dokonca uvádzajú, že je možné využiť niektoré SD karty ako SPI FLASH pre Spartan 6, ja som použil 8MB AT45DB od Atmelu. Tu je treba poznamenať, že datasheet [2] uvádza maximálne veľkosti bitstreamu pre jednotlivé modely Spartanu 6 a treba preto prispôsobiť veľkosť FLASHky.

Obr. 5- Programovacie rozhranie podľa Xilinx-u v móde Master Serial s SPI Flash pamäťou

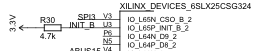

V tomto režime je možné SPI FLASH pamäť naprogramovať priamo pomocou FPGA cez JTAG oficiálnym programátorom od Xilinx-u (funguje to tak, že programátor cez JTAG nahrá do FPGA IP Core, ktorý obslúži programovanie SPI pamäte FLASH). Použitý režim sa volí pinmi M0 a M1 o detailoch ďalších pinov (HSWAPEN, DONE, PROGRAM_B atď) sa dá prečítať v datasheete [2].

Za pozornosť v mojom návrhu beriem jedine použitie pinu INIT_B ako resetu v mojej aplikácií v FPGA.Toto použitie bolo len ako obídenie toho, že som si nevyčlenil na reset samostaný pin a náhodou som INIT_B mal privedený na I/O pin FTDI. Normálne INIT_B slúži na indikáciu či bolo úspešné CRC po načítaní konfigurácie z pamäte avšak našťastie je možné túto funkcionalitu deaktivovať a pin použiť ako bežné I/O .CRC nepotrebujem, pretože ak by nevyšlo CRC, tak sa aj tak konfigurácia nedokončí.

Obr. 7- Pripojenie PROGRAM_B, M0, M1 a SPI rozhrania FLASH

Obr. 8–INIT_B, PROGRAM_B a SPI rozhranie na čipe FTDI pre priame programovanie cez USB

Obr. 9– Zapojenie pamäte FLASH

Obr. 10- Rozhranie JTAG

Druhou možnosťou v mojom návrhu je programovanie za pomoci FTDI priamo z PC, kde sa pomocou FTDI nahrá konfigurácia priamo do pamäte FLASH

s tým, že FTDI podrží pin PROGRAM_B v log. 0 a FPGA všetky I/O uvedie do Hi-Z a tým uvoľní programovanie FLASHky.

Prakticky som používal programovanie cez JTAG pomocou Xilinx Platform Cable USB II, keďže som nemal čas ladiť môj vlastný programátor cez FTDI (kód je zverejnený v C++ , tak ak sa niekomu chce, tak možno nájde tú chybu).

Inicializácia

Pre inicializáciu stačí pomocou FTDI uvoľniť PROGRAM_B z nuly, uvoľniť SPI a FPGA automaticky načíta konfiguráciu z FLASH pamäte.

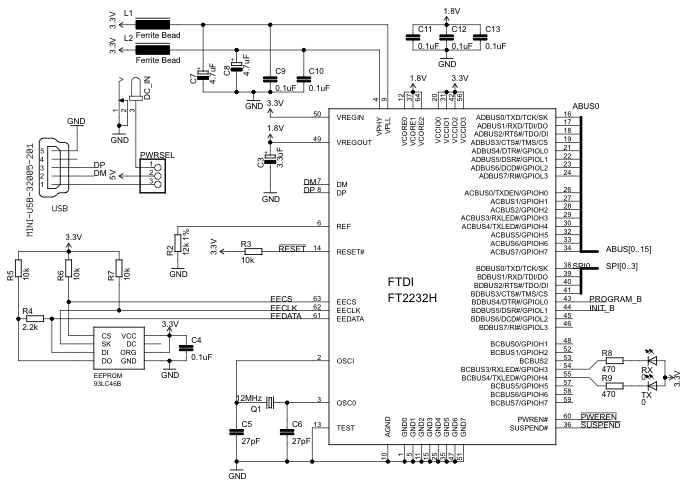

USB komunikácia

USB komunikáciu zabezpečuje (asi väčšine známy) čip FTDI FT2232H, tento čip umožňuje komunikovať na zbernici USB 2.0 a podporuje „High-speed“ čo je plná rýchlosť USB 2.0.

FT2232H disponuje dvoma I/O kanálmi, z ktorých každý podporuje rôzne zbernice ako RS232, RS485, RS422, SPI atď a samozrejme tzv. „bitbang“.

Na to aby FT2232H pracovalo na rýchlostiach USB 2.0, tak používa synchrónnu verziu FT245, ktorá je časovaná hodinami 60MHz, ktoré generujú čip FTDI, tieto hodiny sú využité aj ako hodiny časti logiky v FPGA.

Hodiny do FPGA musia byť privádzané do vstupov globálneho rozvodu hodín (GCLK) inak nie je možné dosiahnuť nijak zvlášť oslnivé rýchlosti (pri použití hodín z iného I/O ako je GCLK môže skončiť dizajn na 10MHz) takže pozor na to. Dôvod je ten, že FPGA disponuje špeciálnymi rozvodmi pre hodiny, ktoré zabezpečujú nízke oneskorenie hodín (clock skew) medzi jednotlivými časťami FPGA.

Jediným zádrhelom pri FTDI bolo to, že po zapnutí FT245 sa vypína kanál B a nie je jasné (podľa dokumentácie) čo sa deje s vývodmi po vypnutí kanálu (čo je kritické pre ovládanie pinu PROGRAM_B), naštastie som mal k zapožičaniu vývojový modul FT2232H, kde som zistil, že sa nezmení po vypnutí ich stav.

Inak je zapojenie FT2232H plne datasheetové, presne ako je zapojený tento modul [5].

Obr. 12- Zapojenie FT245 zbernice na FPGA

Za zmienku jedine stojí, že ABUS13 alebo pin 32 na FTDI nesie 60MHz hodiny a preto je zapojený do GCLK vstupu GCLK30. Ďalej dôvod prečo je zbernica tak chaoticky na schéme rozhodená na piny FPGA – dôvod bol layout dosky, takto vychádzal najjednoduchšie.

EEPROM pamäť je nutná, aby sa dalo prejsť do režimu FT245 a taktiež to umožňuje nastavovať vlastné VID a PID, čo je dôležité na sfunkčnenie FT245 pod Linuxom. V opačnom prípade pre defaultný VID/PID Linux automaticky zavedie do jadra modul, ktorý zablokuje FTDI pre použitie cez knižnicu libftdi. Viac o komunikácii na FT245 rozvediem pri návrhu FW v budúcom článku.

Kompletná schéma programovacieho rozhrania a zapojenia FTDI je tu [6].

Napájacie zdroje

Časť pomerne nezaujímavá, snáď len toľko, že FPGA umožňuje napájať I/O každého „BANKu“ zvlášť. Konkrétne použité FPGA má 4 banky a je teda možné každé napájať inou napäťovou úrovňou (1,8, 2,5, 3,3). Ja som sa uspokojil so všetkými bankami na 3,3V.

Ďalej FPGA vyžaduje napájanie jadra FPGA a to je 1,2V a niektoré a žiaľ aj konkrétne použité vyžaduje VCCAUX na 2,5V, ktoré mimo toho používa aj JTAG.

Čo však je problémom je odhadnúť odber, vzhľadom na to, že závisí od aplikácie v FPGA, tak tu datasheet diplomaticky mlčí a teda jednou z možností je použiť software od Xilinx-u, ktorý odber odhadne podľa návrhu FW alebo zdroje dostatočne naddimenzovať. Keďže som zase nemal k dispozícii odladený FW do FPGA, tak som využil možnosť číslo 2.

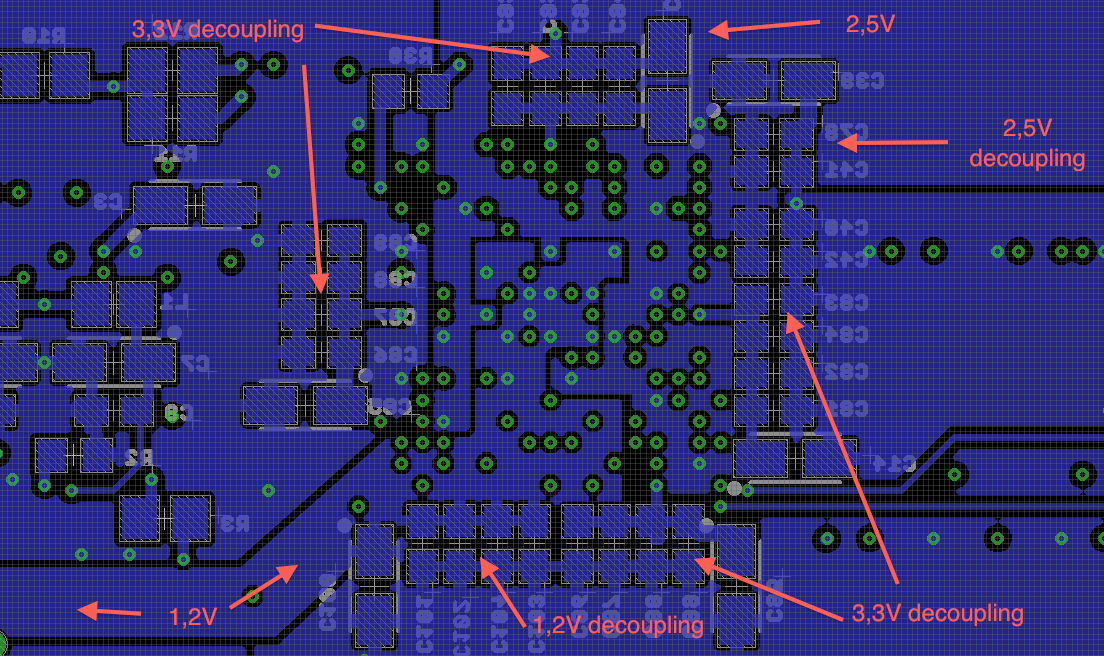

Ďaľšia dôležitá vec je dostatočný „decoupling“ (ak niekto ovláda slovenskú výstižnú alternatívu rád sa ju priučím) – je nutné umiestniť v dostatočnej blízkosti napájacích pinov FPGA banku kondenzátorov, ktoré vyfiltrujú výkyvy odberu FPGA, ktoré spôsobujú to, že sa vnútri spína množstvo logiky. Ja som zvolil pre každý I/O bank keramiky 1x 1000pF, 3x 100nF + 10uF tantal, ďalej to isté pre napájanie jadra (1,2V) a AUX 2,5V.

Ako regulátory z 5V na požadované napätie som použil dva MCP1603T (3,3V a 2,5V) a LM3671 (1,2V).

Schému zapojenia zdrojov je možné nájsť tu [7].

I/O konektory

I/O konektory obsahujú len vývod I/O pinov FPGA a napájacích napätí (3,3V a 5V). Schéma hovorí za všetko [8]. Ďalej sú vyvedené 2 pomocné indikačné LED.

SDRAM

Pripojenie SDRAM si myslím, že tiež nevyžaduje komentár, SDRAM nakoniec nebola používaná, tak popravde neviem či funguje, ale ani nevidím dôvod prečo by nemala. Každopádne schéma [9].

Návrh DPS

V prvom rade nastalo ujasnenie výrobných možností, keďže dosku objednávala škola ,tak bolo vyhradené presne ktorú výrobnú triedu od Pragoboard-u si môžem dovoliť (V skratke: nie buried a blind prechodky, min 0,2mm vŕtanie, max. 4 vrstvy a min 0,2mm clearance/šírka cesty).

Myslel som si, že k návrhu DPS bude veľa čo písať, keďže táto činnosť zabrala veľkú časť času vývoja, avšak v skutočnosti toho nie je až tak veľa a v podstate viem k tomu doporučiť pár praktických rád. Najlepšie sa človek učí keď si to sám vyskúša.. nedá sa to naučiť z čítania. Ďalej odporúčam si pozrieť hotové riešenia, napr. moje alebo toto [11] (čo sa týka návrhu dosky to bolo mojím študijným materiálom, čo sa týka zapojenia, tak k tomu mám výhrady).

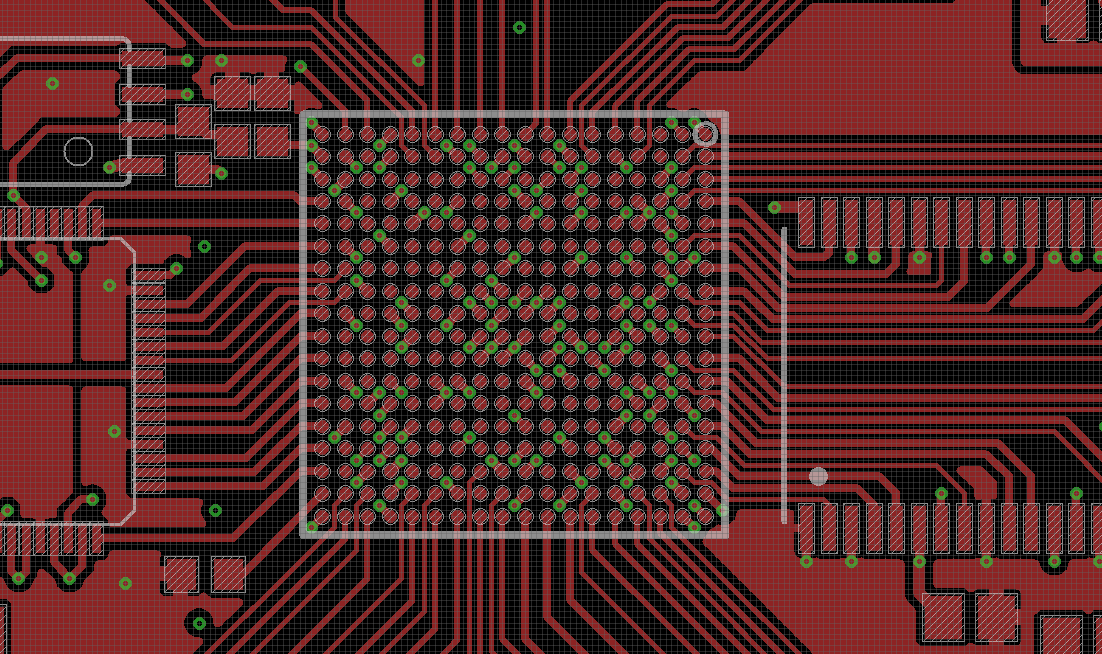

Najdôležitejší je asi tzv. Fan-out vodičov z FPGA. Prvé, čo by som odporučil je pri BGA-čku sledovať, aby boli použité čo najviac vonkajšie vývody, tak aby nebolo nutné vyvádzať vývody z hlbšej úrovne ako 3-tí rad pinov

(preto je nutné sa často vracať k schéme a prerábať, nezabudnúť na to, že hodiny idú len do GCLK atď.). Ak je toto dodržané, tak je možné vodiče vyviesť ešte na vrchnej strane dosky bez použitia prechodiek.

Obr. 13– Vrchná vsrstva, za povšimnutie stojí snaha vyviesť väčšinu na vrchnej strane a spôsob vyvádzania signálov na prechodky pod FPGA.

Samozrejme nie vždy sa to dá dosiahnuť. Napr SPI vývody sú v hlbších radoch. Vtedy je nutné odviesť vodič po vrchnej vrstve do priestoru medzi BGA vývodmi a tam vytvoriť prechodku, nikdy nerobíme prechodky pod BGA pinom (teoreticky to môže fungovať, ale väčšinou sa to tak nezapájkuje pri výrobe).

Dôležité je zamaskovať prechodky pod BGA, aby nevznikli pri spájkovaní BGA skraty medzi ploškami a prechodkami.

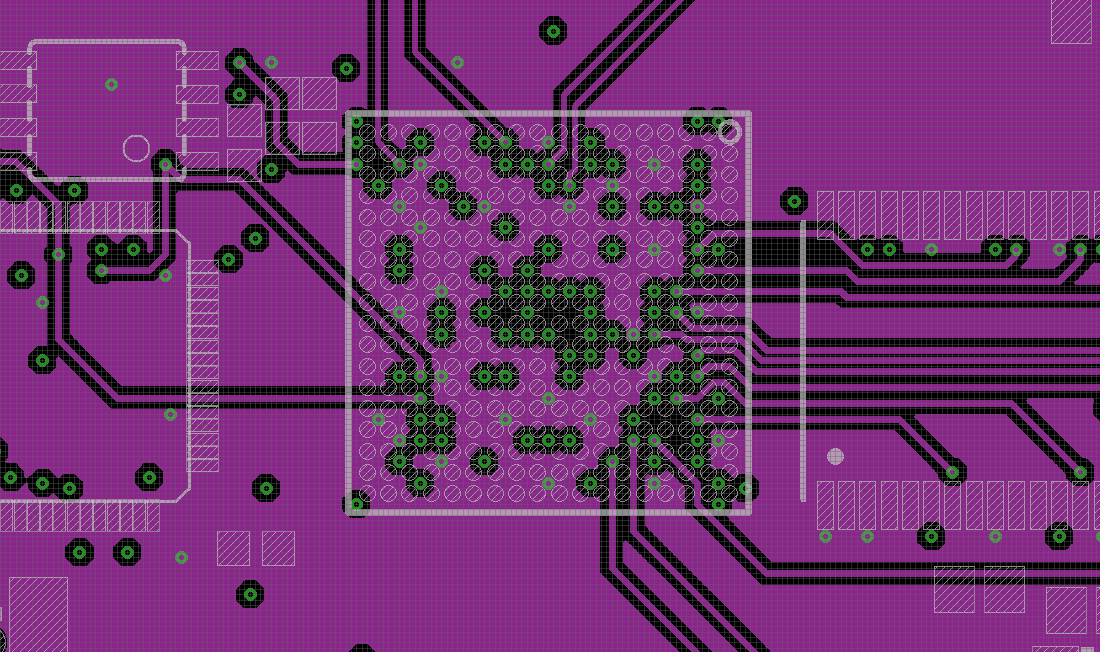

Ďalej zemniace vývody sú vyvedené prechodkami priamo do zemniacej vrstvy.

Obr. 14– Zemniaca vrstva (prvá vnútorná vrstva alebo 2. vrstva), tu sa dá všimnúť že niektoré prechodky smerujú priamo do zemniacej plochy.

Takisto napájanie je riešené polygónmi a napájacou vrstvou (3,3V má vlastnú vrtstu, ostatné sú čiastkové polygóny).

Obr. 15- Vrstva rozvodu 3,3V

Lepšie by bolo mať k dispozícii 6 vsrtiev, kde by mali 1,2V a 2,5V vlastnú vrstvu. Avšak 1,2V ide len do malej oblasti v strede FPGA a 2,5V tiež nepokrýva významnú časť, tak sa to vošlo do disjunktných oblastí na spodnej vrstve.

Obr. 16- Spodná vsrtva, za povšimnutie stojí „decoupling“ každej napájanej časti FPGA

Zvyšok návrhu DPS už nevyžaduje zvláštnu pozornosť, je možné ho nájsť na GIT-e [12] v zdrojovom tvare ako súbory pre Eagle.

Posledné odporúčanie je pre neschopnosť Eaglu, preto treba kontrolovať každú súčiastku ako sa správa vo vnútorných vrstvách. Ja som sa napálil na DC konektore, ktorý mi skratoval oboje vnútorné vrstvy a musel som potom vyškrabávať prechodky nožom.

Obr.17- Správne ohraničine(bot) Obr.18- Nesprávne ohraničenie(in1) Obr.20 – Opravené ohraničenie

Bohužiaľ tento skrat (Obr. 19) DRC neodhalilo (aj keď malo, lebo je tam vďaka frézovaniu – ten malý modrý rámček v tej ploške) a doska bola vyrobená. Aktuálne sa v GIT-e nachádza opravená verzia (Obr. 20).

Analógová časť

Koncepcia

Koncepcia analógovej časti vychádza z potrieb AD prevodníka a transceiveru. V zásade ide o útlmový člen a kompenzáciu sondy, predzosiľňovač. Ďalej napájací zdroj, zdroje referenčných napätí pre AD prevodníky, oscilátor a hodinový buffer.

Obr. 21 – Koncepcia analógovej časti

Vstupná kompenzácia a predzosiľňovač

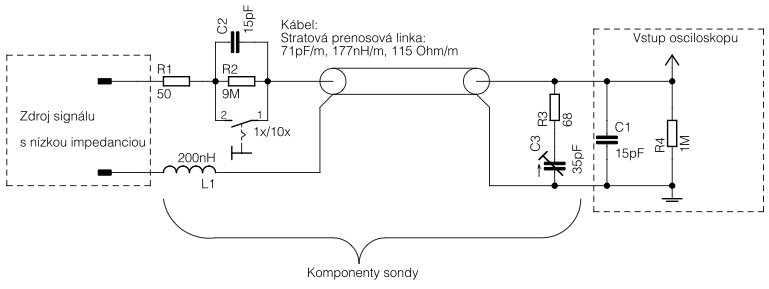

Návrh vstupnej kompenzácie vychádza z vlastností sond. Sondy sa podľa literatúry [10] (to je možné prečítať detailné zdôvodnenie konštrukcie sondy) skladajú z meracieho hrotu, ktorý predstavuje odpor R1 a zemniaceho konektora, ktorý predstavuje indukčnosť L1. Ďalej obsahuje 9MOhm rezistor R2 s paralelne pripojeným kondenzátorom C2 (môže byť premenlivý pre nastavenie kapacitnej kompenzácie), ktoré spolu s prepínačom umožňjú výber útlmu 1:1 alebo 1:10. Potom nasleduje prepájajúci kábel, ktorý tvorí stratovú prenosovú linku. Na záver je sonda tvorená BNC konektorom, ktorý v prípade, že kondenzátor C2 má pevnú hodnotu, môže obsahovať kapacitnú kompenzáciu R3 a C3, čo je aj prípad sondy na schéme na Obr. 22.

Obr. 22 – Schéma typickej osciloskopovej sondy podľa [10]

Prepínanie útlmu medzi 1:10 a 1:1 je zabezpečené odporom R2, ktorý je zapojený v sérii so vstupným odporom osciloskopu a spolu tvoria deliaci pomer. Tento rezistor je možné prepínačom premostiť. Pri vyšších frekvenciách sa však vplyv odporov stráca a deliaci pomer je definovaný pomerom kapacít paralelne zapojených s danými odpormi (C2, C1). Z tohto dôvodu umožňujú nastavenie kapacitnej kompenzácie vstupu osciloskopu a prenosovej linky tvorenej káblom sondy. Toto zapojenie umožňuje, aby sondy pracovali na vysokých frekvenciách, avšak vyžaduje, aby vstup osciloskopu mal vstupný odpor 1MOhm a vstupnú kapacitu blízku hodnote 15pF, aby bolo možné sondu skalibrovať.

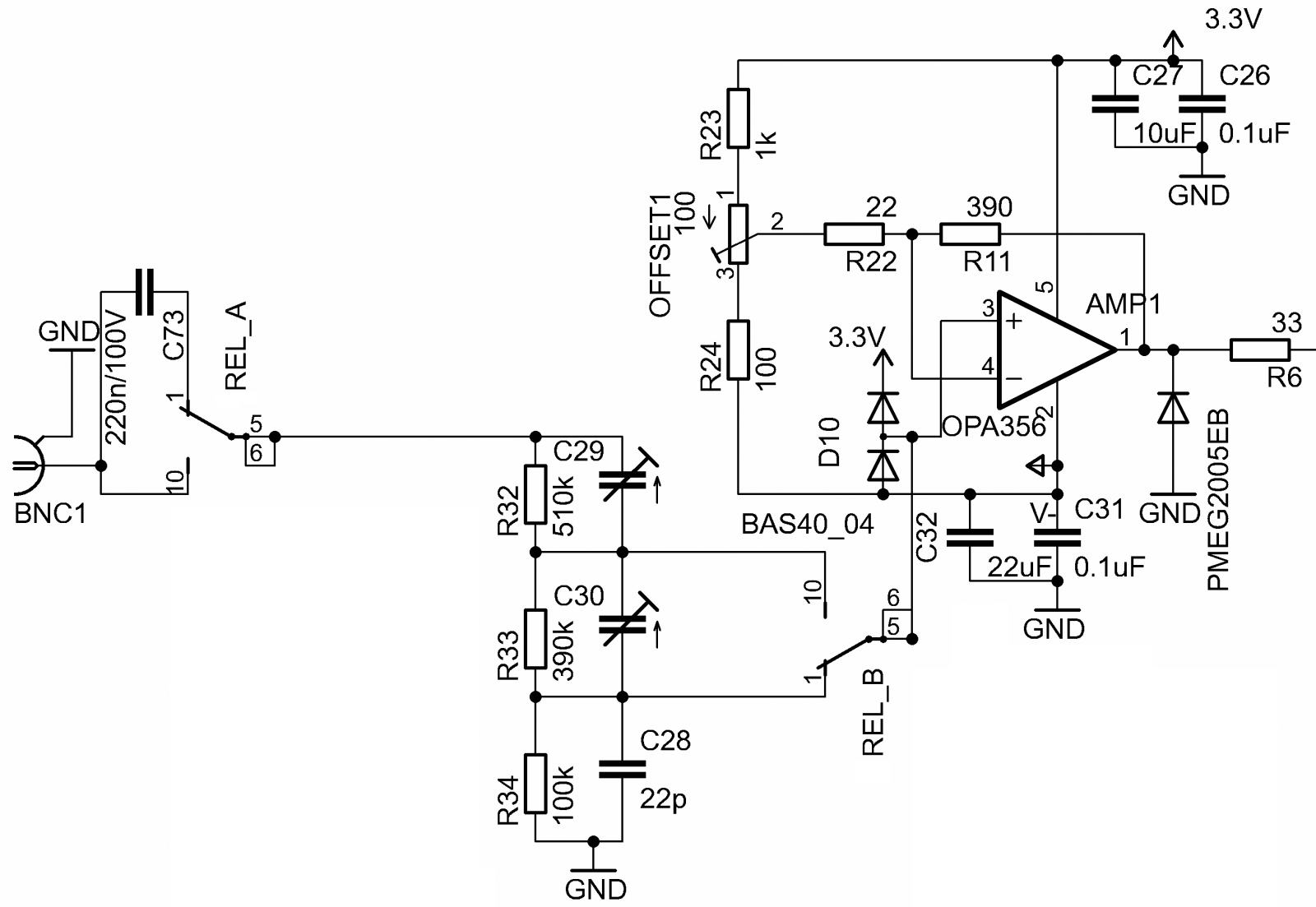

Obr. 23 – Schéma vstupného obvodu osciloskopu

Vstupný signál z konektoru BNC1 najprv prechádza cez kondenzátor C73 alebo priamo podľa toho, ako je nastavené relé REL_A, čo umožňuje vybrať jednosmernú alebo striedavú väzbu. Signál pokračuje na útlmový odporový delič tvorený odpormi R32, R33 a R34 v sérii, ktoré majú spolu odpor ~1MOhm tvoriaci vstupný odpor osciloskopu. Na tieto odpory sú paralelne pripojené kondenzátory C28, C29 a C30 tvoriace vstupnú kapacitu osciloskopu. Kondenzátory C29 a C30 umožňujú nastaviť kapacitu v rozsahu 1-10pF, čo umožňuje dodatočnú kapacitnú kompenzáciu sondy.

Relé REL_B umožňuje vybrať útlm 1:2 alebo 1:10 podľa toho, či sa signál privádza z kondenzátoru C30 alebo C28. Signál z relé je privedený na neinvertujúci vstup AMP1, ktorý je chránený dvojitou Schottkyho diódou D10 proti prepätiu. Zapojenie operačného zosilňovača AMP1 OPA356 vychádza zo zapojení uvedených v dokumentácii OPA356 [13] a doporučeného zapojenia z dokumentácie k AD prevodníku ADC08200 [14]. Bolo však nutné zaviesť možnosť nastavenia offsetu trimrom OFFSET1, aby úroveň výstupného signálu zdvihla z oblasti záporných napätí do oblasti 0-3.3V, ktorú je schopný AD prevodník spracovať.

Vstup AD prevodníka je chránený proti zápornému napätiu Schottkyho diódou. Na to, aby bolo možné spracovať signál zasahujúci do oblasti záporného napätia a zároveň využiť plný rozsah AD prevodníku, je operačný zosilňovač napájaný kladným napájacím napätím 3,3V a záporným napájacím napätím -1V.

Celý návrh bol vykonaný v Spici. Pre zaujmavosť zobrazujem schému v LTSpice (obsahuje kompletný vstup spolu so sondou vrátane kábla simulovaného prenosovou linkou) spolu s výsledkom simulácie.

Obr. 24 – Simulačný model v LTSpiceIV

Obr. 25 – Výsledok simulácie, ako vidieť do 100MHz sa bez problémov predzosilovač spolu so sondou drží v rozmedzi +/- 3dB.

Zapojenie AD prevodníka

Prevodník je zapojený podľa datasheetu[14]. Na odporučenie datasheetu sú digitálne výstupy opatrené 47Ohm odporovou sieťou. Zapojenie inak nevyžaduje nijakú zvláštnu pozornosť.

Obr. 26 – Zapojenie AD prevodníka

Zdroj hodinového signálu pre ADC

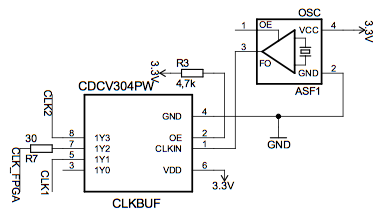

Zdroj hodinového signálu bol relizovaný priamo 125MHz oscilátorom na doske, ktorý je následovaný hodinovým bufferom rozvádzajúcim hodiny do oboch AD prevodníkov a FPGA.

Obr. 27 – Zdroj hodinového signálu

Tu ešte jedna poznámka a to že CLK_FPGA musí byť pripojený na header tak, aby bol pripojený na GCLK vstup FPGA.

Zdroje napätia pre osciloskopickú časť

Pre AD prevodníky a predzosilňovač treba 2 ďalšie zdroje a to zdroj záporného napätia -1V pre predzosiľňovač a zdroj referenčných napätí pre AD prevodník.

Ako zdroj záporného napätia (nábojová pumpa) je použtý čip LT1054L zapojený podľa datasheetu [15].

Obr. 28 – Zdroj napätia -1V.

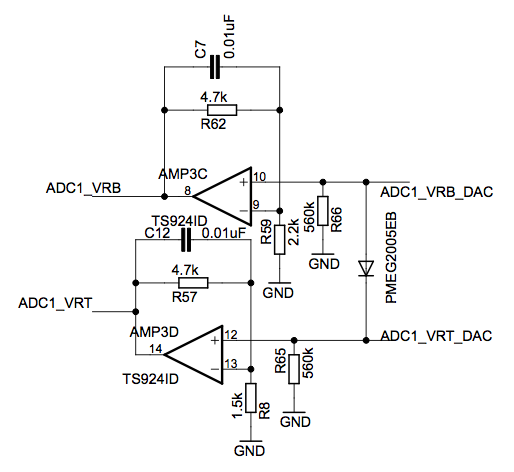

Ako zdroj referenčných napätí je použitý operačný zosiľňovač v spolupráci s DAC, čo umožňuje v softwari nastaviť zisk a offset zmenou referenčného napätie ADC.

Za každým výstupom DAC následuje 15kOhm, ktorý funguje ako ochrana, aby v prípade nastavenia vrchného referenčného napätia nižšieho ako spodného neodpálilo DAC cez ochranu vo vstupe následujúcich OP zosilňovačov. Pri ladení bola táto hodnota znížená na 5kOhm z dôvodu zvýšenia stability referenčného napätia.

Obr. 30 – Zapojenie operačného zosiľňovača zabezpečujúceho zdroj referenčného napätia, za povšimnutie stojí ochranná Schottkyho dióda, ktorá zabraňuje nastaiť VRB vyššie ako VRT

Logický analyzátor

Aby bolo možné snímať digitálne signály rôznej napäťovej úrovne, je nutné túto úroveň previesť na jednotnú úroveň 3.3V, ktorú používa FPGA.

Toto zabezpečuje transceiver spolu s nastaviteľným zdrojom napätia, ktorý umožňuje v SW vybrať logické úrovne na ktorých meraný obvod pracuje. Vybratý ransceiver podporuje 5V, 3.3V, 2.5V a 1.8V logiku, jumperom je možné vybrať napájanie transceivera z externého obvodu.

Obr. 31 – Zapojenie transceivera

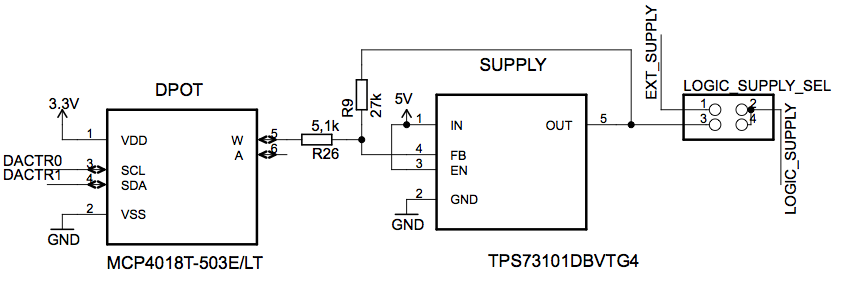

Digitálne nastaviteľný zdroj je realizovaný nastaviteľným napäťovým regulátorom, ktorý má v spätnej väzbe zaradený digitálny potenciometer. Digitálny potenciometer sa nastavuje cez zbernicu I2C.

Obr. 32 – Digitálne nastaviteľný zdroj

Návrh DPS

Návrh DPS pre analógovú časť nie je nejak zvlášť (v porovnaní s FPGA) zaujímavý. Je to dvojvrstová doska s obojstranne osadenými súčiastkami. Jediné o čo som sa snažil je skrátiť analógové cesty čo najviac a zároveň dosiahnuť čo najlacnejšiu výrobnú triedu v Pragoboarde (tak, aby sa to dalo vyrobiť v tzv. Pool servise). Určité rady sú v datasheete od ADC [14], tie doporučujem dodržať.

Ďalej by som odporučil menej nahustiť niektoré komponenty, hlavne keď to osádzate ručne (dôvod bol taký, že keď som nechcel lepiť súčiastky na spodnej strane pri pájkovaní v reflow peci), ale každopádne sa to dalo osadiť aj tak, ako to bolo, len som na určité miesta pridával kondenzátory a to bol trochu problém ak tam bolo málo miesta.

Záver

Týmto uzatváram dnešný dieľ, všetky schémy si je možné pozrieť tu [16] prípadne na GIT-e [12].

V ďalšom diely sa zameriam na HDL jadro, ktoré je v FPGA a celkovo vývoj a ladenie FW pre FPGA. Ak by niekoho zaujímali hlbšie detaily ,tak môžem článok doplniť, ale už ma nenapadá čím, takže môžem zodpovedať prípadné dotazy pod článkom.

Literatúra a odkazy

[1] – https://svetelektro.com/clanky/fpga-od-zadania-k-produktu-uvod-i-613.html

[2] – https://www.xilinx.com/support/documentation/user_guides/ug380.pdf

[3] –https://www.xilinx.com/support/documentation/

sw_manuals/xilinx11/pim_c_introduction_indirect_programming.htm

[4] – https://www.youtube.com/watch?v=7AFGcAyK7kE

[5] – https://dangerousprototypes.com/docs/FT2232_breakout_board

[6] – https://www.dropbox.com/sh/cy4ldah24slzdpa/abJiUvJXYK/digital1.pdf

[7] – https://www.dropbox.com/sh/cy4ldah24slzdpa/DcNXvRsvnE/digital2.pdf

[8] – https://www.dropbox.com/sh/cy4ldah24slzdpa/ISzYbeQ6tL/digital3.pdf

[9] – https://www.dropbox.com/sh/cy4ldah24slzdpa/rij2zEcCzX/digital4.pdf

[10] – https://www.dfad.com.au/links/THE SECRET WORLD OF PROBES OCt09.pdf

[11] – https://danstrother.com/2011/01/16/spartan-6-bga-test-board/

[12] – https://github.com/josko7452/qwave-project

[13] – https://www.ti.com/product/opa356

[14] – https://www.ti.com/product/adc08200

[15] – https://cds.linear.com/docs/en/datasheet/1054lfg.pdf

[16] – https://www.dropbox.com/sh/cy4ldah24slzdpa/zRzbHfkyo1

[17] – https://merlin.fit.vutbr.cz/FITkit/

- FPGA od zadania k produktu – Hardware II. - 5. septembra 2013

- FPGA od zadania k produktu – Úvod I. - 19. augusta 2013

Komentáre (4)

Pridaj komentár

Prepáčte, ale pred zanechaním komentára sa musíte prihlásiť.

Parada, pekny clanok, zavana to skutocnou elektronikou 🙂 Inak, decoupling capacitors su blokovacie kondenzatory; decoupling je blokovanie.

Díky :).. jaj keď človek furt číta anglické zdroje, potom aj na materčinu zabudne, od budúca používam náš ľubozvučný výraz 🙂

Výborný článok, dúfam že bude ďalšie pokračovanie. Je mi jasné, že pre tých 5 ľudí čo vedia o čom to je sa neoplatí to písať, ale pre nadšencov ako som aj ja je to pekné čítanie.

Keď mi skončí tento zabijácky semester tak to dopíšem.. žiaden strach… už som sa dostal aj do VLSI a Standard cell designu v jedej firme tak to bude na dlhšie.. ale rátam že žiaľ najskôr na Vianoce 😉